ISSN: 1832-5505 Vol-11 Issue-03 Sep 2023

# EFFICIENT 32-BIT BCD ADDER USING QUANTUM DOT CELLULAR AUTOMATA

L. RANGA SWAMY, ASSISTANT PROFESSOR, ranar404@gmail.com

T. RANJITHADEVI, ASSOCIATE PROFESSOR, ranjitha.svitece@gmail.com

N.A.V. PRASAD, PROFESSOR, navp.vlsi@gmail.com

Department of ECE, Sri Venkateswara Institute of Technology,

N.H 44, Hampapuram, Rapthadu, Anantapuramu, Andhra Pradesh 515722

**Abstract---** It is essential in today's technological world that systems be small and lightweight, and that they handle data quickly and with little delay. We need a fresh strategy to meet these demands when we construct these circuits.

A new method of design called Quantum-dot Cellular Automata (QCA) is introduced in this article. With QCA, there is room for substantial advancement in the design of more complex circuits. In this paper, we propose a novel method for designing 32-bit BCD adders based on QCA. Topics covered include binary coded-decimal adders, decimal arithmetic, low power, majority gates (MG), and quantum-dot cellular automata (QCA).

# INTRODUCITON

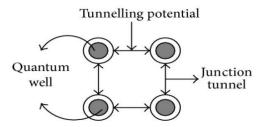

The basic limit will be approached by CMOS with continued and rapid dimensional scaling. Additionally, existing CMOS technology devices are limited in their ability to scale further due to short channel effects, high power dissipation, and quantum effects [2-3]. New device technologies are able to circumvent the scaling constraint of CMOS technology. Some of the technologies that fall within the category of "Beyond CMOS" are SETs, QCAs, and RTDs, or resonant tunnelling diodes. We recommend Quantum-dot Cellular Automata over all of these developing nanotechnologies. You can get a device density of 1012 devices/cm2 and an operating speed of THz using QCA, a transistor-less computing paradigm. By using the quantum effects of tiny scale, the QCA device paradigm supplants logic based on field effect transistors. A quantum-dot cellular automaton is a way to achieve device performance via the coupling of cells that represent binary information but do not conduct current.

This Paper is Organized as follows Section II will gives you the details of the software used to prepare this project, Section III deals with the Structure of QCA cell and its polarization and QCA background Section IV gives you the design and implementation efficient 32-bitBCD adder, Section V deals with the outcome of the project and finally Section VI gives the Conclusion and Future Scope & some of the references of this project.

#### I. SOFTWAREUSED

QCA designer is the product of an ongoing effect to create a rapid and accurate simulation and layout tool. for quantum-dot cellular automata (QCA). It is capable of simulating complex QCA circuits on most standard platforms. And it is an ongoing research effect by the Walus Lab at the University of British Coloumbia to create a design and simulation tool for QCA. This tool is still under development and is provided free of cost tothe research community "as is". QCA is an emerging concept in computational nanotechnology for the realization of computer using arrays of nano-scale QCA cells. These QCA cells are capable of performing all complex computational functions required for general- purpose computation (majority function, Inversion, and fan-out). The QCADesigner tool facilitates rapid design, layout and simulation of QCA circuits by providing powerful CAD features available in more complex circuit design tools.

ISSN: 1832-5505 Vol-11 Issue-04 Oct 2023

Fig. 1 Structure of a QCA Cell

The most fundamental element of the QCA structure is shown in figure 1. It is the building block of the QCA technology. As we can see in the figure it is having four dots at all its corner. The structure has two free electrons. The structure of the QCA in provided in the figure 1.

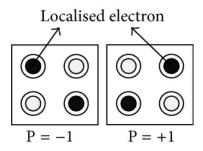

Binary "0" binary "1"

Because of the coulombic repulsion these two electrons can only be placed in two stable states. The electrons are always resided in diagonally opposite corners of the QCA cell. The diagonally opposite corners are having maximum distance. The stable states also called as polarization. As perthe locations of the electrons in the cell two states can be take place. These states are considered as binary states 1 and 0. For the purpose of explanation the figure 2 is shown.

The diagonally opposite electrons interact to each other by the electrostatic forces and due to this force the electrons maintain its polarization. However the QCA cells cannot flow the data intrinsically therefore to get the control over flow of the direction of electrons the four clock zones are associated. These four clock signal have 90° phase difference. The QCA design is partitioned into clock zones. The clock scheme, named the zone clocking scheme, makes the QCA designs different polarizations intrinsically pipelined.

# 32 BIT BCD ADDER

ISSN: 1832-5505 Vol-11 Issue-04 Oct 2023

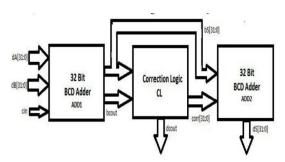

Fig 3.Structure of the 32 bits BCD adder.

In brief this proposes a unique approach to develop a QCA- based 32 bits BCD adder which can achievehigher computational speed than existing counterparts with occupying less area or count cell. The novel 1-digitdecimal adder generates, propagates, and absorbs

a carry signal with delay times up to 27%, 45%, and 44% lower than the faster existing counterparts that are those described in differently from all previous works, we extended our work to the design of a 32-bits QCA-based BCD adder.

The BCD adder here presented follows the traditional top-level structure illustrated in Fig. 3, but it exploits the novel logic expressions demonstrated in the following by Equations 1 and 2.

As the main result, the proposed

#### III. OUTPUT

Fig 1 digit BCD adder in QCA.

approach leads to the best trade off between the overall occupied area and thespeed performances.

To understand the new design strategy, let us examine first the 4 bits binary adder ADD1. 4 bit binary adder ADD1 collects the value of input dA(3:0) and dB(3:0) as well as its carry "cin" and figure out its binary outputas bS(3:0) and "bcout", this whole process it carried out as per the equation (2a) that introduces only one Majority gate(MG) between Ci and Ci+1.

Generally BCD means Binary Coded Decimal as we know decimal values means 0-9 so that if the output of the BCD adder result is greater than 9 or when the carryis "1" then we Add 6 to the obtained output to get the valid BCD Value. The reason for to add 6 to the UNBCD output is the in hexadecimal the difference between the maximum value and to the 9 is 6. And this 32 bit BCD adder consists of 2 32bit binary adders and correction logic which consists of AND & OR gates .

So here the QCA implementation shows that we need4 full adder at the top of the block for adding two 4bit binary numbers and there is a correction logic which consists of AND& OR gates.

And we need 3 Full Adders at the bottom to add 6 0r 0 to the output of the first 4 full adders.

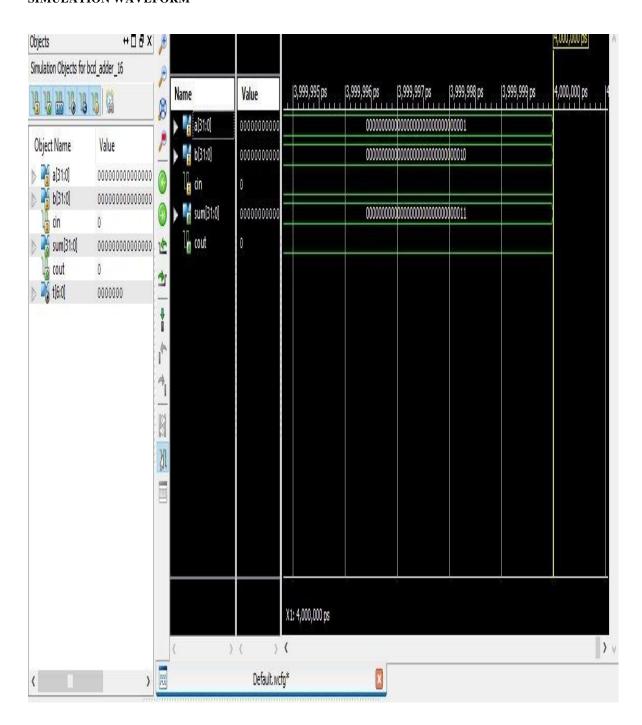

Generally we developed 1 digit BCD adder in QCA due to circuit complexity and increase in th SIMULATION WAVEFORM

ISSN: 1832-5505 Vol-11 Issue-04 Oct 2023

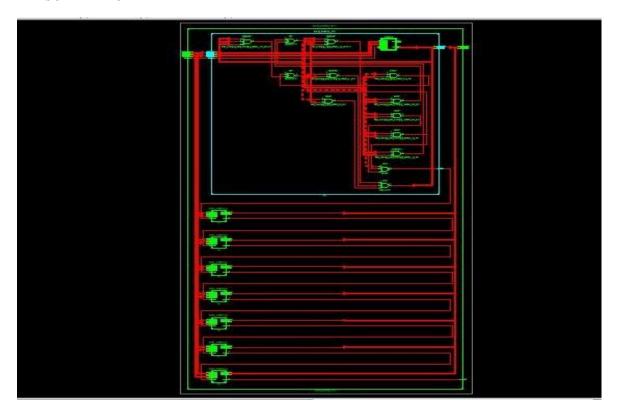

#### RTL SCHEMATIC

The figure shows the RTL schematic of the 32 bit BCD adder In this we have first developed an VHDL code for the 4 bit BCD adder then with the help of this 4 bit BCD adder we have developed 32 bit BCD adder

Here we have used Eight 4 bit BCD adders the output of one 1 digit BCD adder is added as the Carryin to next 1 digit BCD adder and at last the output of the 8th BCD adder is taken as cout.

#### VI.CONCLUSION

In order to create a 32-bit BCD adder, the proposed work primarily focuses on combining two 32-bit BCD adders using binary adders. If the result is not a valid BCD value, an additional 6 is added to the total. This allowed us to create the BCD adder's simulation waveforms and RTL schematic.

### REFERENCES

In their 1993 article "Quantum cellular automata," C. S. Lent, P. D. Tougaw, W. Porod, and G. H. Bernestein discuss this topic in Nanotechnology, volume 4, issue 1, pages 49–57.

[2] "Problems in designing with QCAs: Layout=timing," International Journal of Circuit Theory and Applications, vol. 29, pp. 49-62, 2001, by M. T. Niemer and P. M. Kogge.

In a 2009 article published in the Microelectron Journal, K. Navi, M. H. Moaiyeri, R. F. Mirzaee, O. Hashemipour, and B. M. Nezhad discussed two novel complete adders that use majority-not gates and operate at low power.

"Adder design and analyses for quantum-dot cellular automata," published in the May 2007 issue of the IEEE Trans. Nanotechnol., by H. Cho and E. E. Swartzlander Jr., pages 374–383.

5. "Serial parallel multiplier design in quantum-dot cellular automata" by H. Cho and E. E. Swartzlander Jr., published in 2007 in the Proceedings of the IEEE Symposium on Computer Arithmetic, pages 7–15.

# Applied GIS

ISSN: 1832-5505 Vol-11 Issue-04 Oct 2023

In the 2009 IEEE Nanotechnol. Mater. Devices Conf., S. W. Kim and E. E. Swartzlander Jr. presented a paper titled "Parallel multipliers for quantum-dot cellular automata."

Multipliers with coplanar crossings for quantum-dot cellular automata, by S. W. Kim and E. E. Swartzlander Jr., published in 2010 in the Proceedings of the IEEE International Conference on Nanotechnology, pages 953-957. [8] "Montgomery modular multiplier design in quantum-dot cellular automata using cut-set retiming," in Proceedings of the 2010 IEEE International Conference on Nanotechnology, pages 205-210.

"QCA systolic matrix multiplier," in Proceedings of the IEEE Annual Symposium on Very Large Scale Integration, 2010, pages 149–154, by Lu, Liu, O'Neill, and Swartzlander, Jr.

The paper "Matrix multiplication using quantum-dot cellular automata to implement conventional microelectronics" was published in the September 2011 issue of the IEEE Trans. Nanotechnol. and was co-authored by J. D. Wood and D. Tougaw.